CMS® Cloud

全寿命周期元器件选型管理软件 CMS® Cloud 是一款全寿命周期元器件选型管理平台,基于 Ai 人工智能 与 “混合云” 部署,可与 Altium Designer、Cadence 、Siemens EDA 等主流 EDA 设计工具及 PDM/PLM/ERP 等系统集成,该系统管理全部的电子元器件数据,包括元器件属性、符号、封装、三维模型等,设计师通过该软件选用元器件开展电路设计,设计完成后输

全寿命周期元器件选型管理软件 CMS® Cloud 是一款全寿命周期元器件选型管理平台,基于 Ai 人工智能 与 “混合云” 部署,可与 Altium Designer、Cadence 、Siemens EDA 等主流 EDA 设计工具及 PDM/PLM/ERP 等系统集成,该系统管理全部的电子元器件数据,包括元器件属性、符号、封装、三维模型等,设计师通过该软件选用元器件开展电路设计,设计完成后输

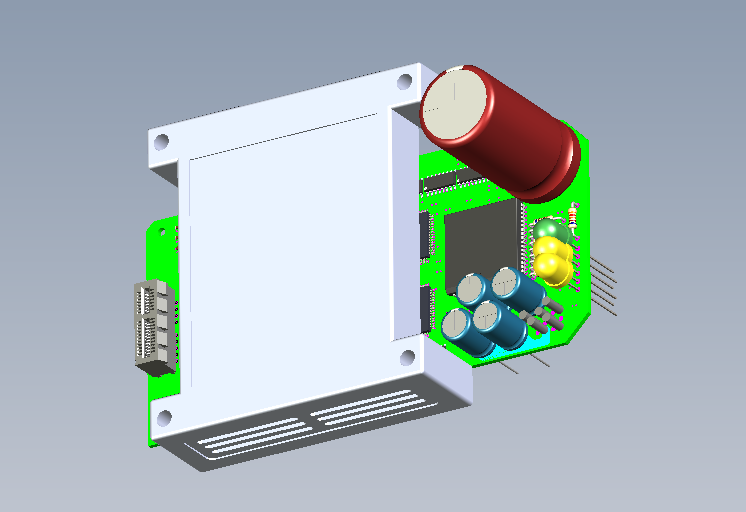

CMS® ECAD-MCAD Librarian是北京迪浩永辉自主研发的AI智能全三维电子元器件建模软件,专为电子研发企业解决传统建库效率低、规范不统一、人工误差大等痛点。依托AI与OCR图像引擎,实现原理图符号、PCB封装及三维模型的自动识别及生成,大幅提升研发效率、降低生产成本。

CMS® Allegro Analyser 电路设计项目在线评审软件是专门应用于对电路设计多人实时在线评审的工具软件,与 EDA 设计软件完全无缝集成。 通过 PCB 设计项目在线评审及管理软件,评审专家可随时随地在设计文件中精确坐标点上创建批注,问题描述、严重等级及改进建议均被结构化记录,形成清晰的“问题清单”。 CMS® Allegro Analyser 电路设计项目在线评审软件基于Clien

CMS STDDOC智能标准化出图以及校验系统是帮助客户高效的规范化管理自己的设计成果,进而与CMS Cloud或者用户的专家知识库管理软件集成有效的推进知识传承。CMS STDDOC智能标准化出图以及校验系统是基于官方发布的技术标准(如ISO5457,GB/T5489,GB/T 6988,GB/T 18135,WJ 3-2011,GB148,GB10609.4,GB/T 13361,Q/AP(J

CMS Design Plus套件依托Cadence Allegro原生态的设计环境,集成SiPA和PCBA设计检查分析要求的所有知识库规范,提供一体化SiP/PCB快速“设计-检查-再设计”的快速迭代式设计,丰富的检查类型设定能胜任产品设计的多样性检查,并具有设计师和工艺师等角色权限的交叉检查分析,这些过程均体现在SiP Layout以及Allegro PCB设计过程中而不是依赖第三方辅助工具

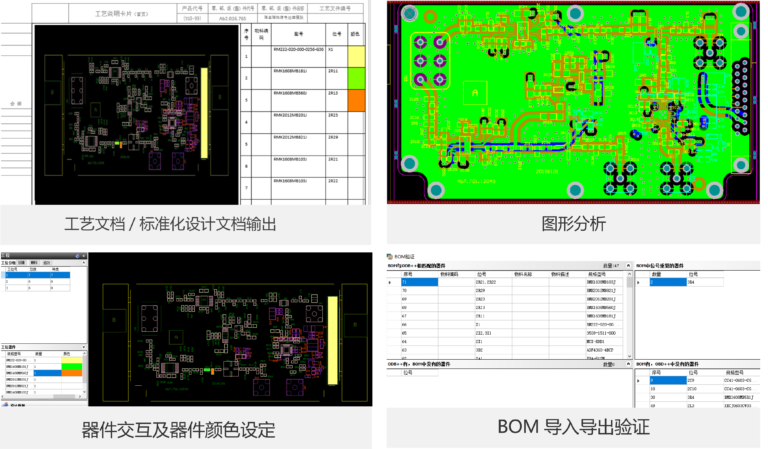

CMS ProDOC是一个图形处理引擎软件,它能满足用户从设计到工艺的数据智能分析,用户也可在此软件引擎构建各种应用,包括工艺文档处理,工艺BOM与设计BOM验证,生产虚拟组装,整板器件交叉定位,并可实现与CAPP/MES/PDM产品生产制造信息化系统集成等。 功能特点: 支持EDA数据导入,兼容主流设计工具格式。 支持BOM数据的导入导出及验证,确保与PCB数据保持统一。 支持器件全局搜索和

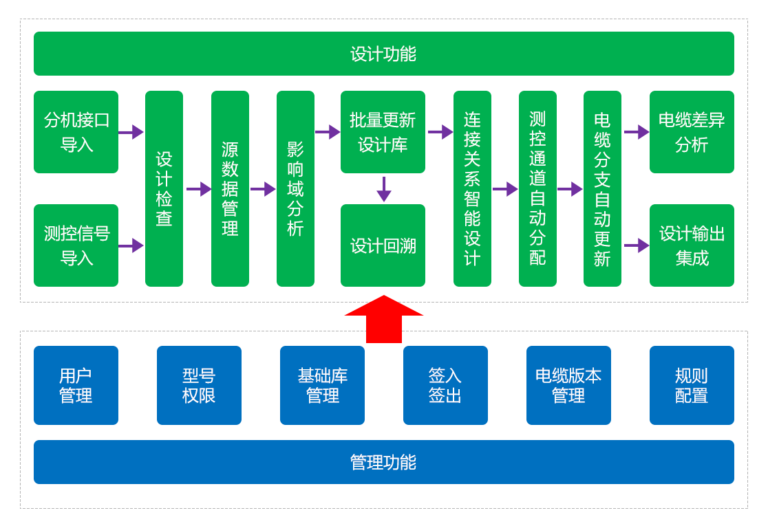

对于复杂电子系统产品的电气设计,从硬件架构层次来看,都是由多个部件或者多个电路板组成的系统。因此,对于电气产品的硬件研发过程,包含: 系统的电气(线缆网)系统设计、单板设计、电气电路仿真分析、系统仿真分析等。

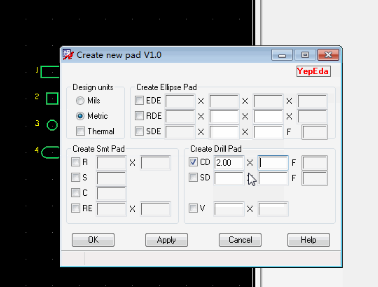

提供与Cadence Allegro PCB集成的设计检查和设计增强功能,覆盖了快速化设计定义、快速设计检查、快速设计建库和快速输出等功能。 该模块基于AXL-Skill脚本语言开发,与Cadence工具菜单无缝集成,实现在PCB设计环境的初始化,快捷布局布线设定,约束环境定义、电气规则检查和DFX工艺规则在线分析检查,输出检查报告。 软件界面: 软件安装完成后,分为Yep Designer、La

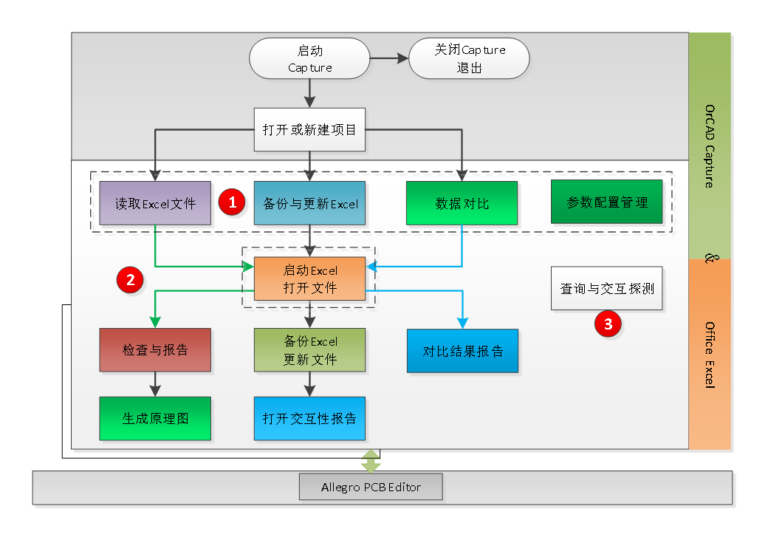

CMS® IO Designer复杂电气原理图快速设计工具可以实现基于CAD/CAE设计工具的自动化I/O设计互连转换过程,帮助工程师快速进行设计图纸与在线互连性检查更新,改善了设计过程因过多的人工肉眼参与导致的错误,从而大幅提高复杂系统电路互连的设计效率。 当工程师接到复杂电气母板或系统电路互连互通的设计任务时,会面临诸多电气连接端子设计、复杂模块的I/O信号定义与修改、信号互连匹配性检查,这些

当设计师在处理微系统组件设计时,会面临诸多如外框图形、复杂器件图形和微带结构、多层腔体结构等设计时,需要通过手动反复进行导入和导出并确认设计发生正确的变更,该过程需要人工反复的数据的交互和检查,费时费力容易出错。微波系统快速设计CADPlug工具提供了从CAD图形快速切入到CAE设计环境的一键图形处理优化设计工具,包括数据快速导入导出模块、层面的同步显示模块、集成菜单模块、数据检查与报告模块、增强