Cadence Sigrity QIR2 更新 | Common Features

本文描述了Cadence® Sigrity™产品QIR2 的新增功能。

Common Features

本节介绍QIR 2中多个Cadence® Sigrity™ 2017工具共同的新增功能。

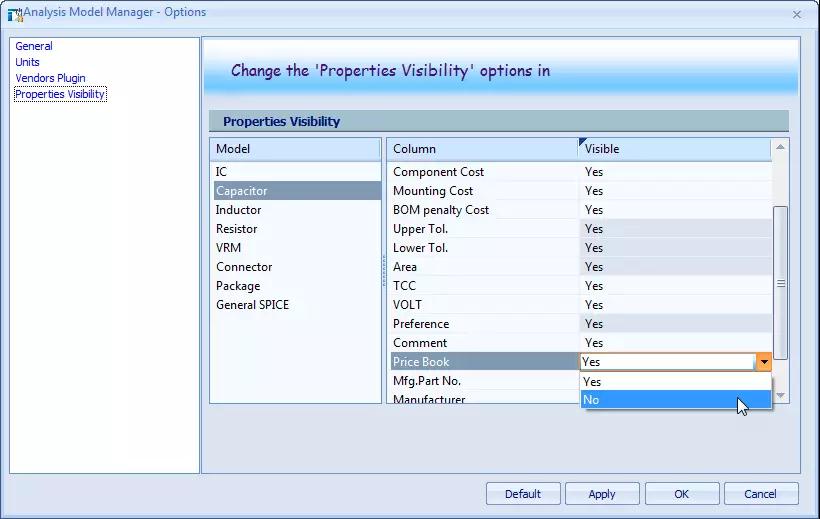

分析模型管理器

AMM中列可见性的设置

Options对话框中提供了新的设置,使您可以隐藏选定的列。蓝色表示的单元格不能被隐藏。

新的Tcl命令

添加了用于搜索、删除库、查询和模型分配的新Tcl命令。

转换器增强

本节介绍如下转换器增强功能。

通用材料文件

Sigrity 2017QIR 2和Allegro 17.2 QIR 5版本现在完全支持新的基于XML的material.cmx文件格式。为设计定义和分析,使用通用文件可保持更高的一致性,并确保更新的材料属性应用于整个组织架构中。

对传统文件格式的支持仍然可用。然而,如果Allegro数据库以新格式保存,则Sigrity应用程序将支持在打开Allegro数据库时找到材料定义。

material.cmx文件可以在Sigrity安装目录中找到

(

新支持的格式

Zuken CR8000 (*.sdf, .stf) 和IPC2581 (.xml) 文件格式现在可以在Sigrity应用程序中转换和打开。

PowerTree

PowerTree在该版本中进行了以下更新。

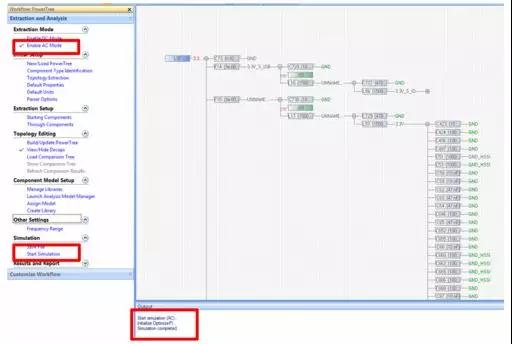

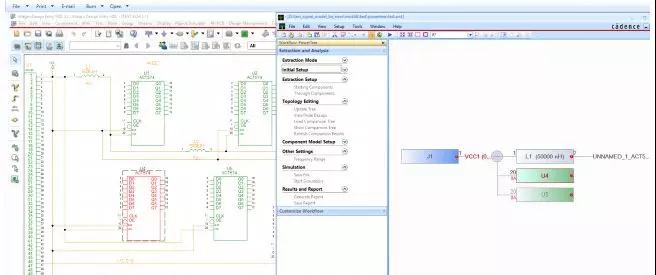

基于工作流程的PowerTree增强功能

从这个版本开始,开发了一个新的工作流程,提取和分析,用户可以更方便地使用PowerTree。AC和DC模式均可支持。

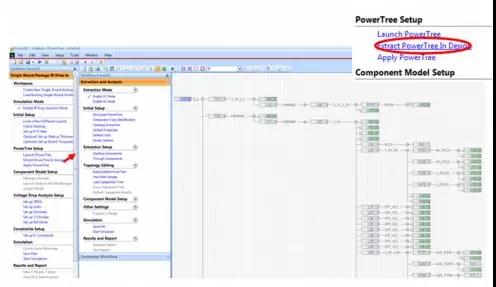

从Sigrity工具生成PowerTree

PowerTree现在支持直接解析spd设计,基于SPD数据,获取连接的拓扑。此功能已集成到PowerDC和OptimizePI中。工作流程中已新增步骤Extract PowerTree In Design来实现此功能。

注意:只可从SPD中提取元器件的连接关系,所有属性需要在PowerTree中手动添加。

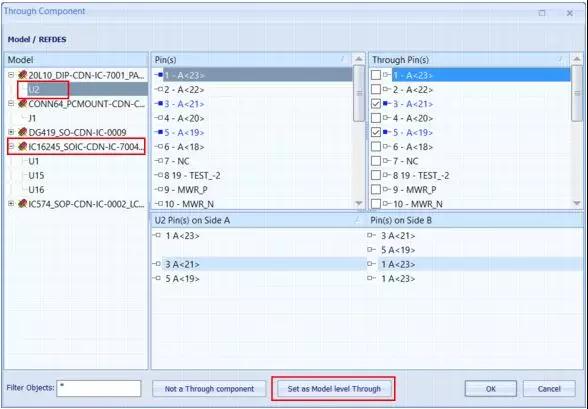

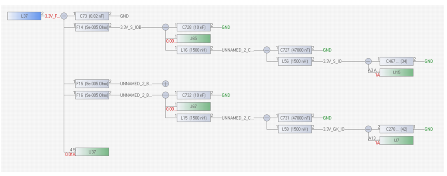

支持器件级别连通器件和VRM/Sink属性

在该版本中,可以使用元器件和VRM / Sink属性在器件级别设置模型。

有相同模型的不同器件可能有:

- 不同连通信息

- 不同属性(如VRM电压、sink电流)

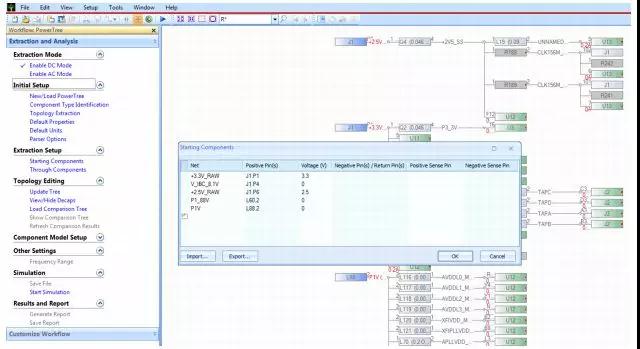

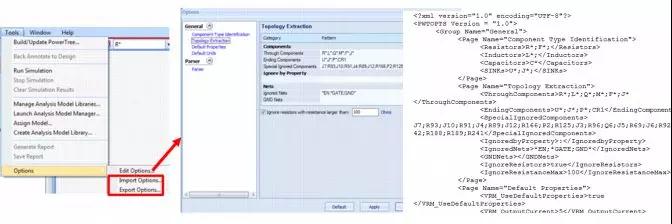

PowerTree的导入/导出设置和选项

该版本中,PowerTree中新增了以下新选项:提供导入和导出选项以生成PowerTree(.xml文件)

起始器件的导入和导出选项(.csv文件)

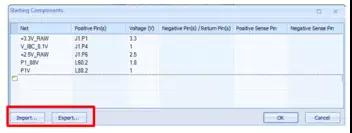

在PowerTree中运行预布局AC仿真

在该版本中,您可以直接在PowerTree中运行AC仿真。

注意:运行仿真需要OptimizePI的license。

PowerTree / DEHDL交叉检测支持

从这个版本开始,在PowerTree中选择一个实例会自动高亮并放大显示DEHDL中相应的实例。这个功能在DEHDL中也是一样的。

PowerTree的TCL支持

在这个版本中,PowerTree实现了一些新的TCL命令,这些命令有助于自动化以及与其它工具的集成。有关TCL命令的更多信息,请参阅“TCL脚本参考”。

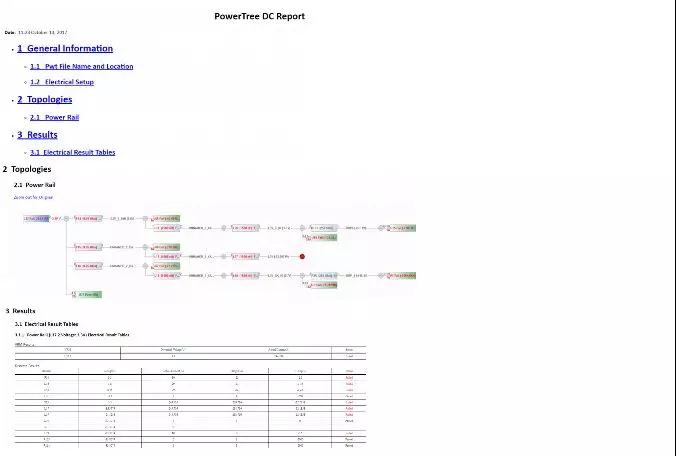

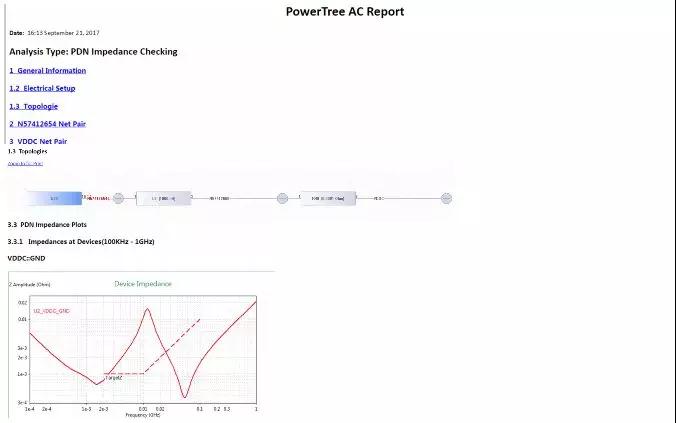

生成HTML报告

从这个版本开始,仿真之后可以在PowerTree中生成DC和AC的HTML报告。

以下是DC报告的示例:

以下是AC报告的示例:

其它的可用性改进

在该版本中,在PowerTree中添加了以下与可用性有关的改进功能:

- 折叠分支的符号更大

- 新的缩放区域图标

- 对去耦电容块的数据提示改进

走线检查改进

ERC - Trace Impedance/Coupling/Reference Check workflow可用于SPEED2000™,PowerSI®, Allegro® Sigrity™ SI, OrCAD® Sigrity ERC。

本节介绍以下走线检查改进功能。

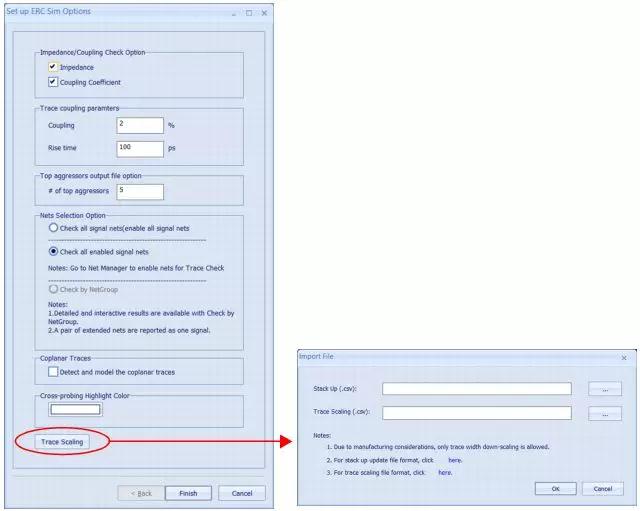

Trace Scaling 支持

Set up ERC Sim Options窗口中添加了Trace Scaling按钮。

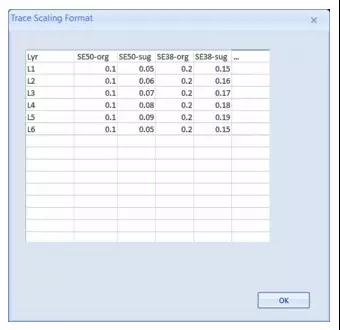

对于trace scaling文件的格式,在“导入文件”窗口的Notes部分单击相应的超链接。信息会显示在Trace Scaling Format窗口中。

随着走线宽度的变化,layout中会显示阻抗变化。

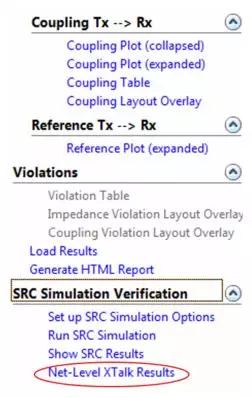

基于网络的XTalk

现在可以通过在SRC SI Metrics Check中直接调用Level-2仿真来计算和报告基于网络的串扰。