文档中心

CMS Suite Datasheet

电子技术日益发展,加快了电子设备产品更新换代,每个电子设备生产企业都管理了大量与电子物料相关的设计信息、生产信息以及元器件信息等,而企业掌握的这些信息不能在企业发挥最大的利用价值。

物资编码混乱、物资分类没有建立最优的标准、型号规格不正确、性能参数不完善、生产商管理不到位、数据流程不规范、企业综合管理系统(如ERP/MRP/PDM等)中整理好的元器件相关信息与设计人员无法有效智能化沟通都阻碍着信息一体化具体实施。

Allegro高级教程之基于Xnet的网络等长设置

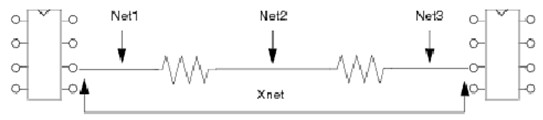

由无源、分立器件(电阻、电容、电感)连接起来的几段网络的组合称为Xnet,如图:

本文介绍在Allegro中如何创建一组Xnet并设置这组Xnet等长。

关键字:高速电路、网络等长设置、XNET、XNET等长、传输延迟、Allegro线长控制

数据转换之Altium Designer原理图到OrCAD Capture的转换-

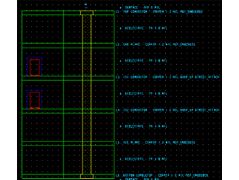

Allegro基础教程之PCB外形尺寸标注模块介绍

Allegro允许用户进行多种类型尺寸的标注,例如线性标注、角度标注、直径/半径标注、元件次序标注等。本文就Allegro的尺寸标注环境做系统介绍。

关键字:Cadence教程、Allegro教程、Allegro PCB、Allegro技术专题、尺寸标注

Allegro基础教程之Allegro后处理方法之Thieving功能介绍

Thieving是指在PCB设计中添加覆铜点或取样点的操作技术,是为了保持PCB在电镀时板上各点镀铜厚度均匀,避免该区域铜箔过度电镀的情况发生。

添加的取样点以过孔形式表示,执行Thieving命令后,软件自动添加取样点,如图:

关键字:Cadence教程、Allegro教程、Allegro PCB、PCB设计、thieving

Allegro高级教程之高速设计规则约束管理

对于高频电路而言,势必会产生传输线效应和信号完整性问题,怎样利用PCB的布线来保证整个高频系统实施是设计关键。为了避免高速电路的传输效应,必须严格控制关键网络的走线长度,合理规划走线的拓扑结构。本文就针对高速电路中的布线规则约束做一个系统的介绍。

关键字:Cadence教程、Allegro教程、Allegro PCB、PCB设计、PCB约束、高速电路、高速PCB、线长控制、等长控制、延迟设置、网络拓扑结构、阻抗匹配

Allegro高级教程之元件嵌入式布局解决方案(Embedded Components)

Allegro中元件嵌入式布局设计分为以下几个步骤:

1、设置Embedded_Placement属性,只有附带该属性的元件才能进行嵌入式布局;

2、设置嵌入式板层;

3、设置嵌入式摆放约束规则;

4、实现元件嵌入式布局。

关键字:Cadence教程、Allegro教程、Allegro PCB、PCB设计、元件嵌入布局、元件内嵌、微型化电路板设计、高密度电路板设计、Embedded Components

Allegro基础教程之Allegro后处理方法之丝印(Silkscreen)

为了方便PCB板的安装,所有元件、安装孔都要有对应的丝印标号。本文主要介绍Allegro中丝印的生成方法。

关键字:Cadence教程、Allegro教程、Allegro PCB、PCB设计、丝印、Silkscreen