产品中心

集成封装设备-半自动倒装焊机

半自动倒装焊机(Semi-auto Flip-chi Bonder)本装置是半自动型低成本倒装焊机,通过人眼把搭载平台上放置的基板的标志点与搭载头吸着的芯片的标志点对齐后,通过热压着的方式键合。

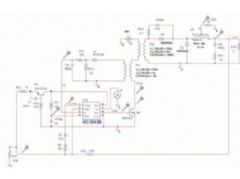

Power IC Spice Model

通过高速周期性(high-speed cycle-by-cycle)的仿真来展示真实的大信号性能,采用最新的精确建模技术进行电流模式控制仿真;进行CCM和DCM转换器仿真;分析控制系统的环路增益,输入滤波器的设计和分析;对所有主要器件进行功率损耗测量和电应力分析。总之,通过建模和仿真您可以对整个电源系统进行完整的模拟。

主要特点

分析大信号产生的影响,例如启动瞬态、功率级半导体承载应力和负载阶跃响应• 研究变压器、电源转换器、滤波器和控制电路在不同结构下的实现方法• 计算器件承受电应力,测试剩余功率损耗• 比较电路特性与线性或非线性磁力的差异• 分析电路时域、频域特性• 不限制电路规模来模拟和分析电源系统对于Cadence PSpice技术,功率器件模型库囊括了200多个时域仿真模型用于电力电子设计。设计者可以插入代表实际器件的模型并在特定运行环境下对其进行开关性能的仿真。

IBM EMSAT SI/PI Rules Check

EMSAT-SI是一个SI/PI规则检查程序,可以导入流行的版图文件,并且快速检查PCB设计中违反SI/PI规则的地方。用户可以为SI/PI指定多种多样的关键网络/器件,如I/O网络,电源/地网络,时钟网络,去耦电容。EMSATA-SI通过对SI/PI关键网络的挨个检查,摆脱了枯燥的人工检查,并大大减少了人工错误。待规则检查完成后,违反SI/PI的部分可参在Allgero,EMSAT-UV,HTML文档中图形化显示。